Dr. P. Papazoglou combines imagination, art, and engineering to create unique educational tools and demystify complex topics in academic classes.

Prof. P. Papazoglou is also an active hardware/software designer/developer and his interests are in the areas of immersive technologies for transforming the existing conventional approaches in education.

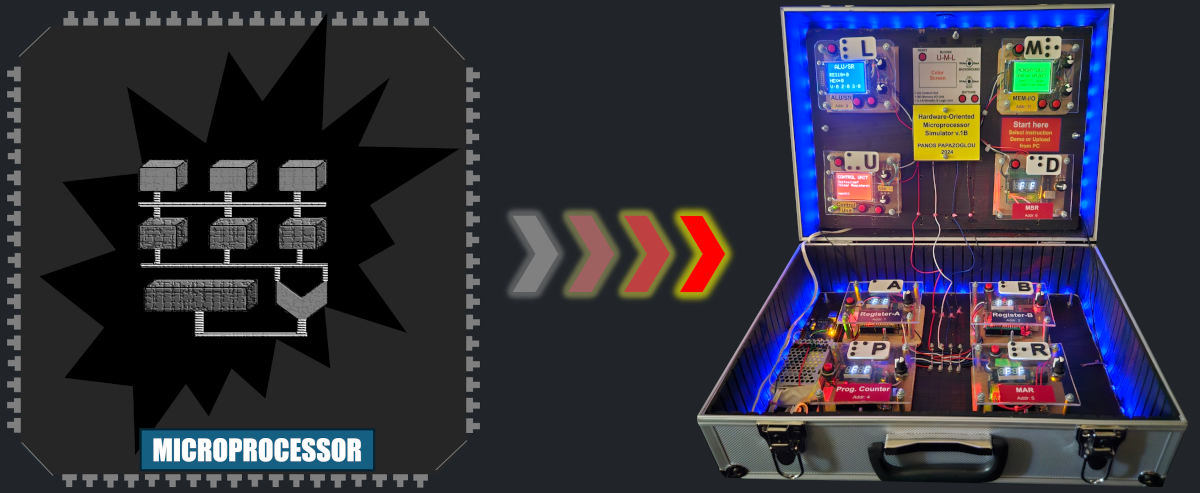

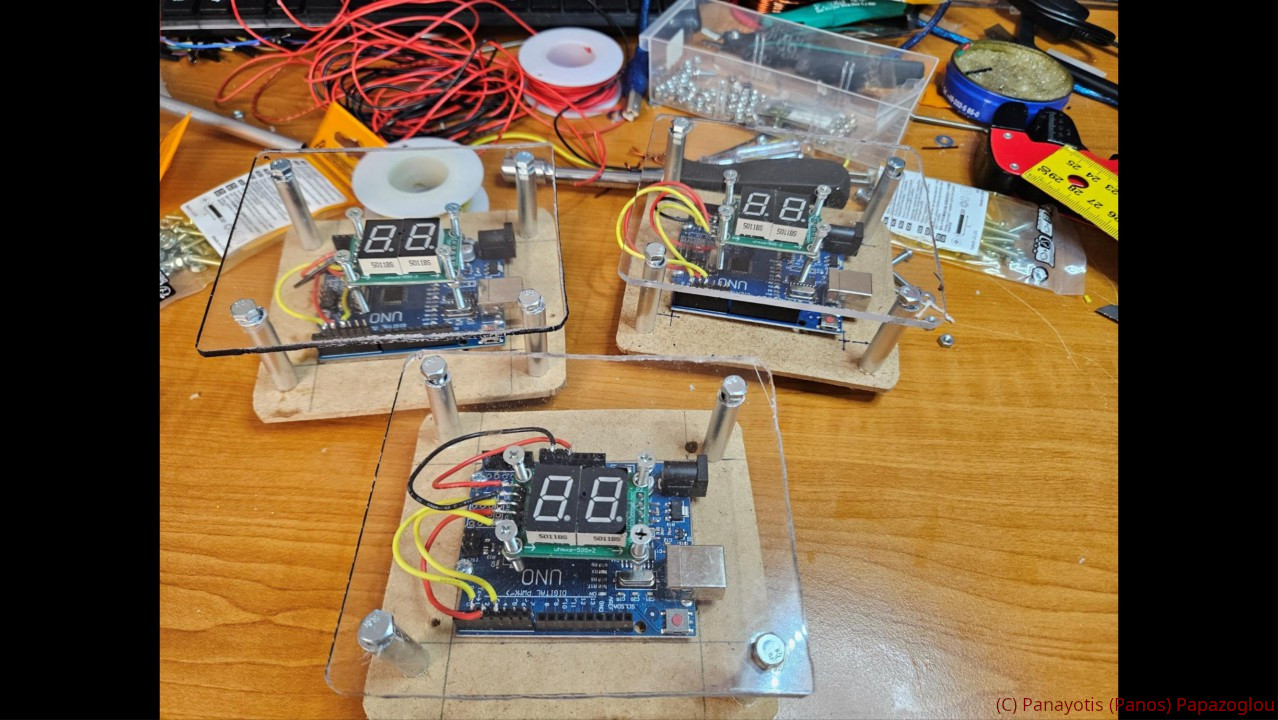

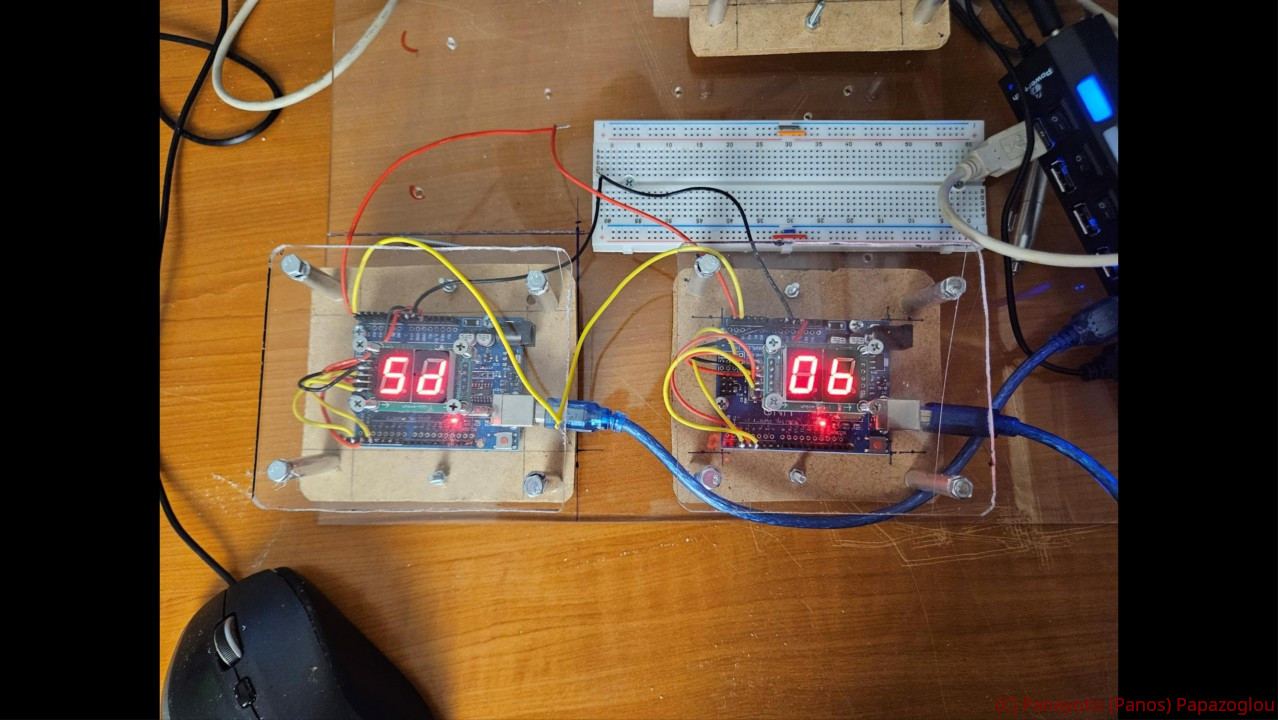

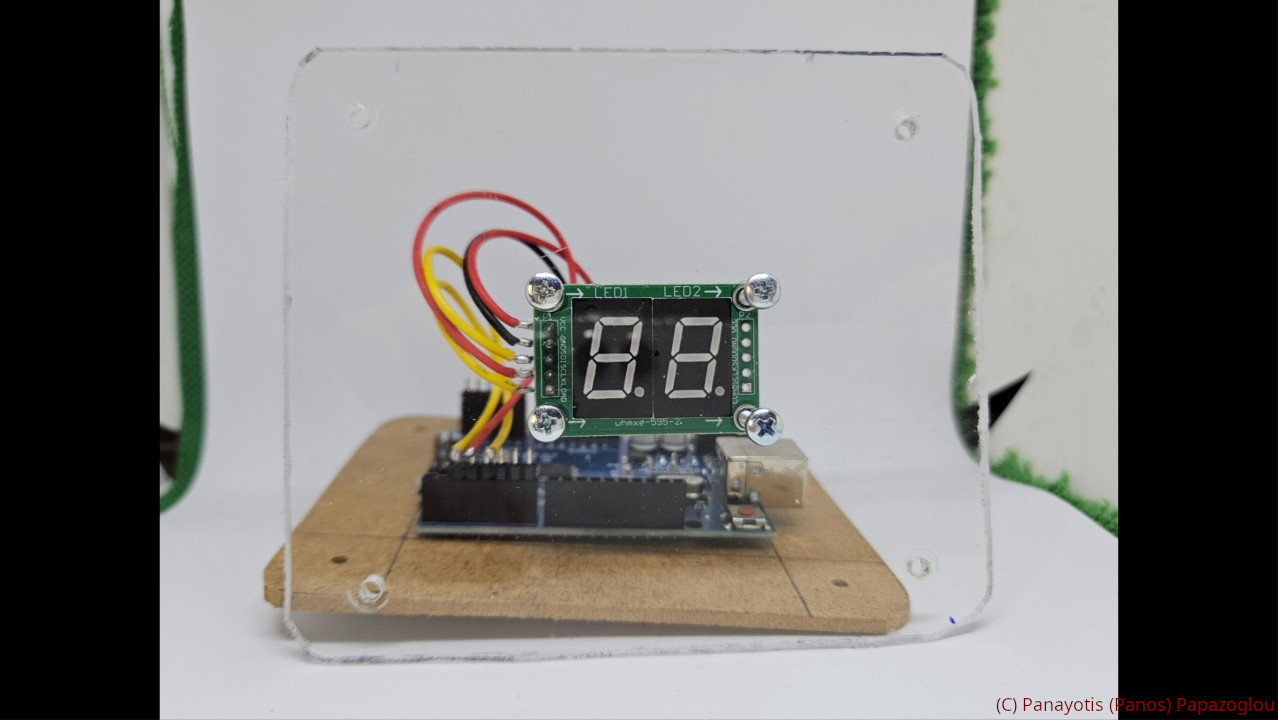

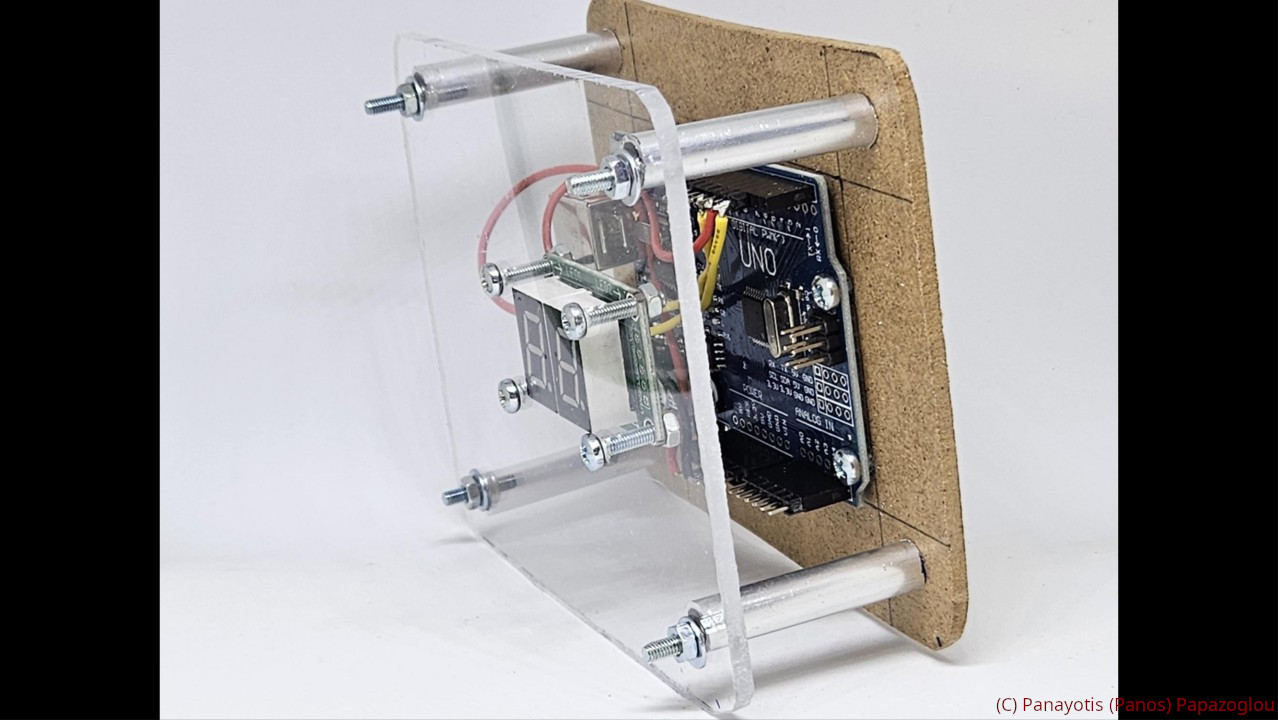

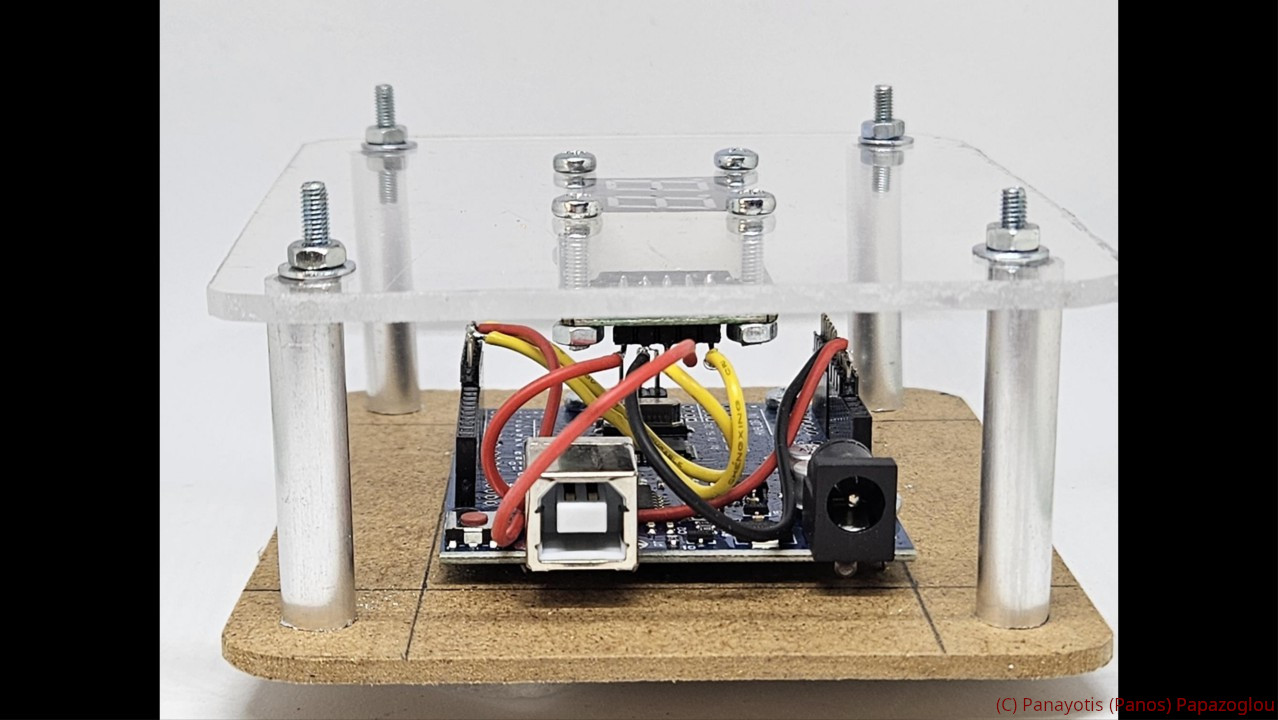

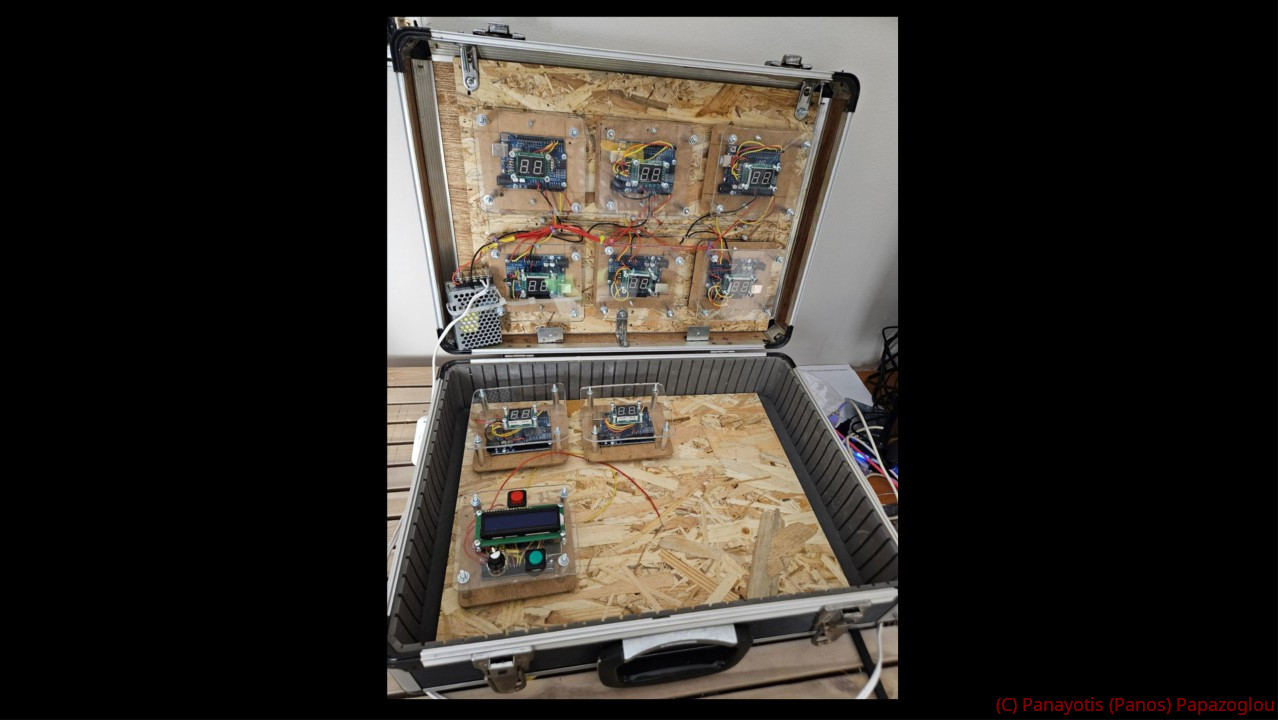

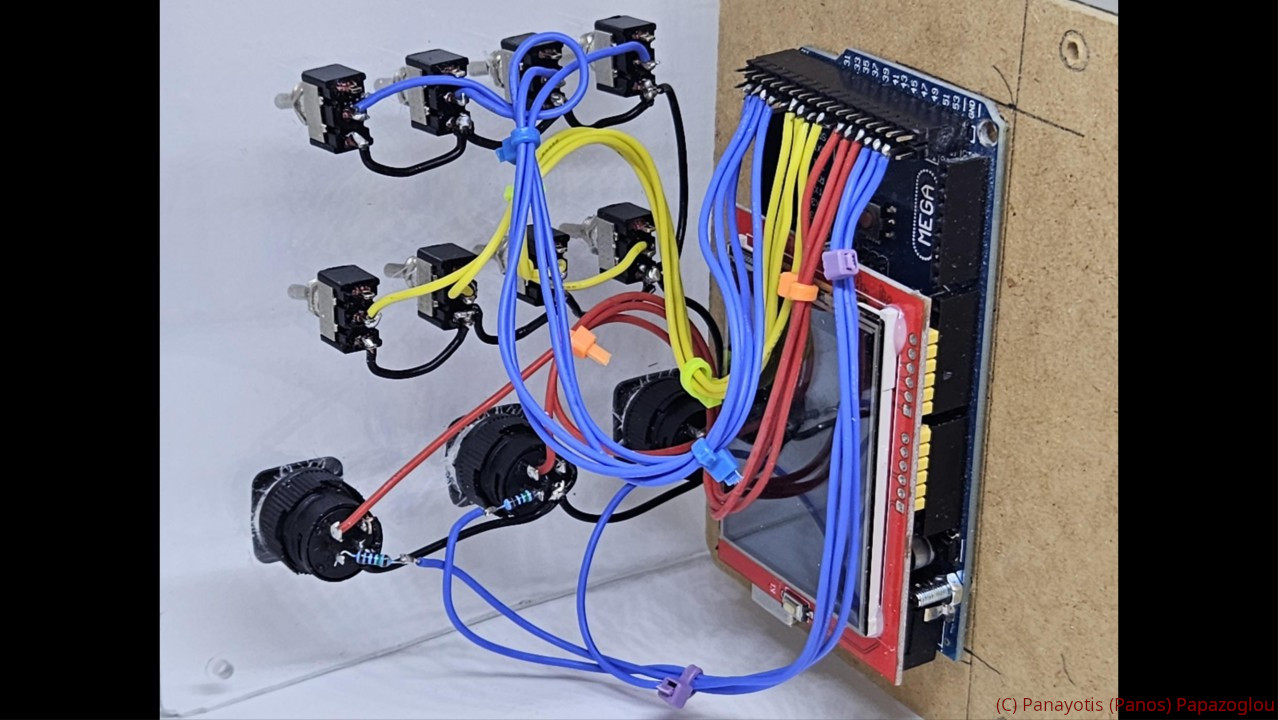

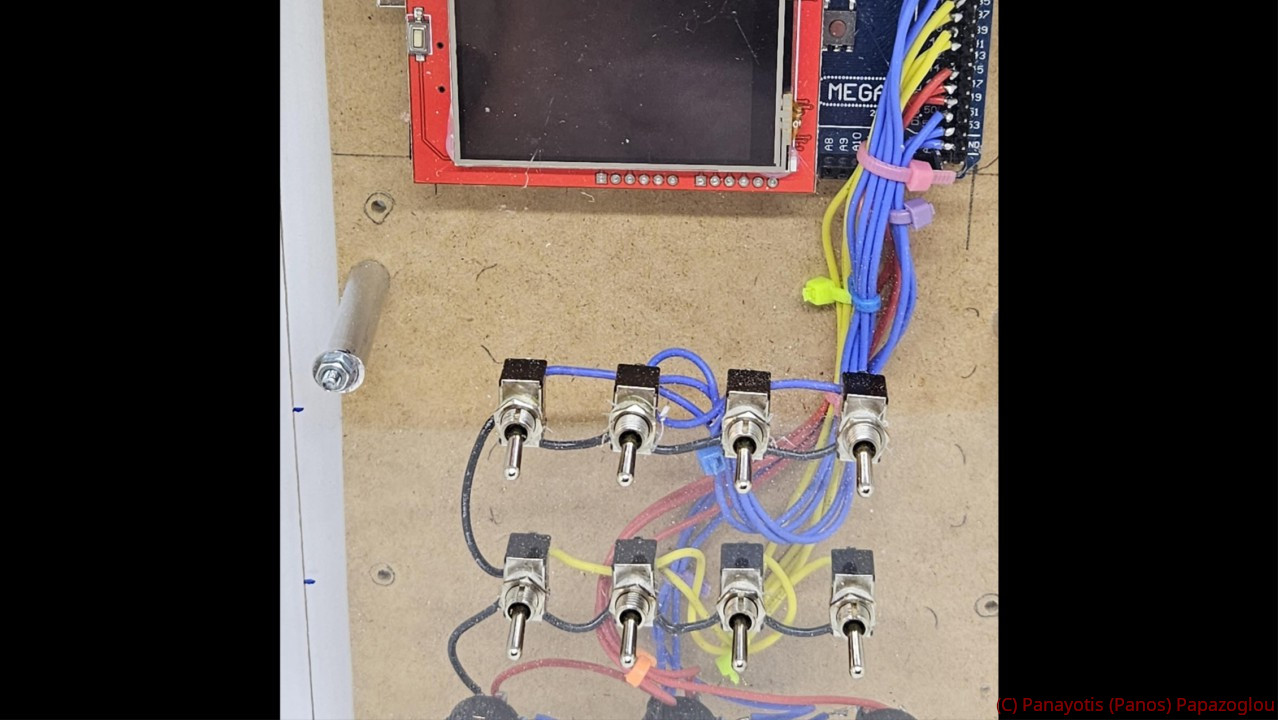

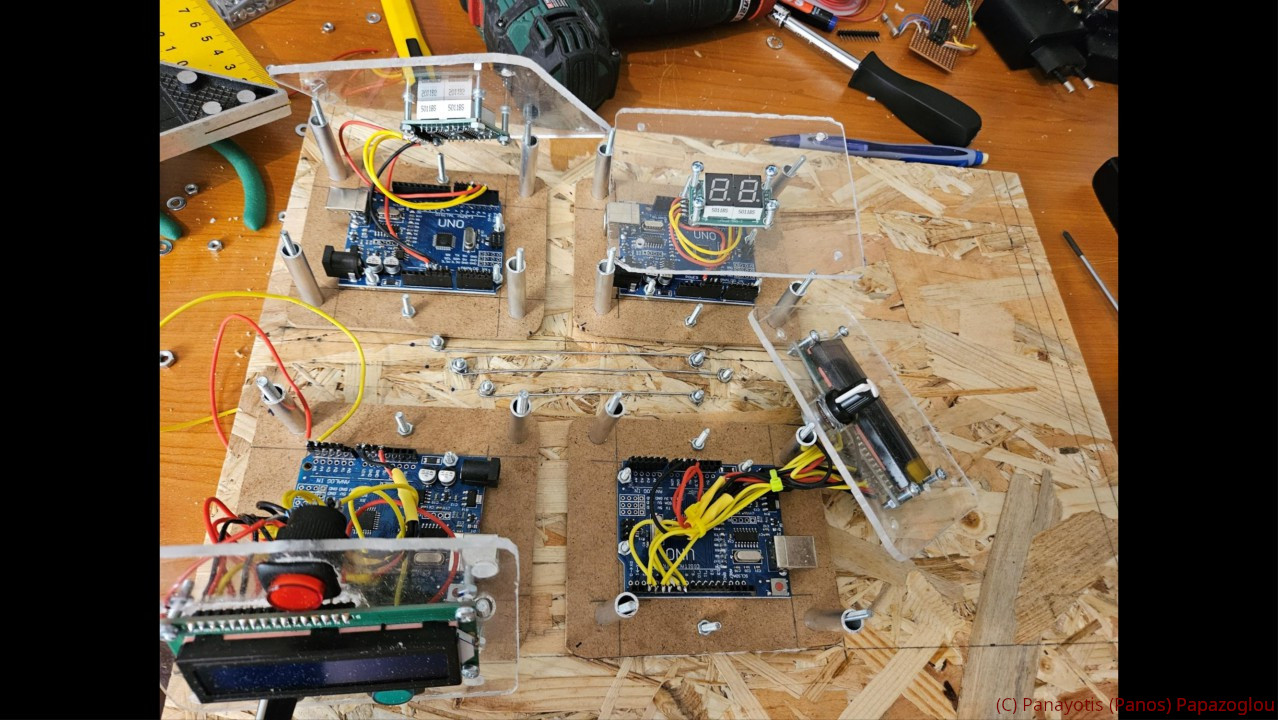

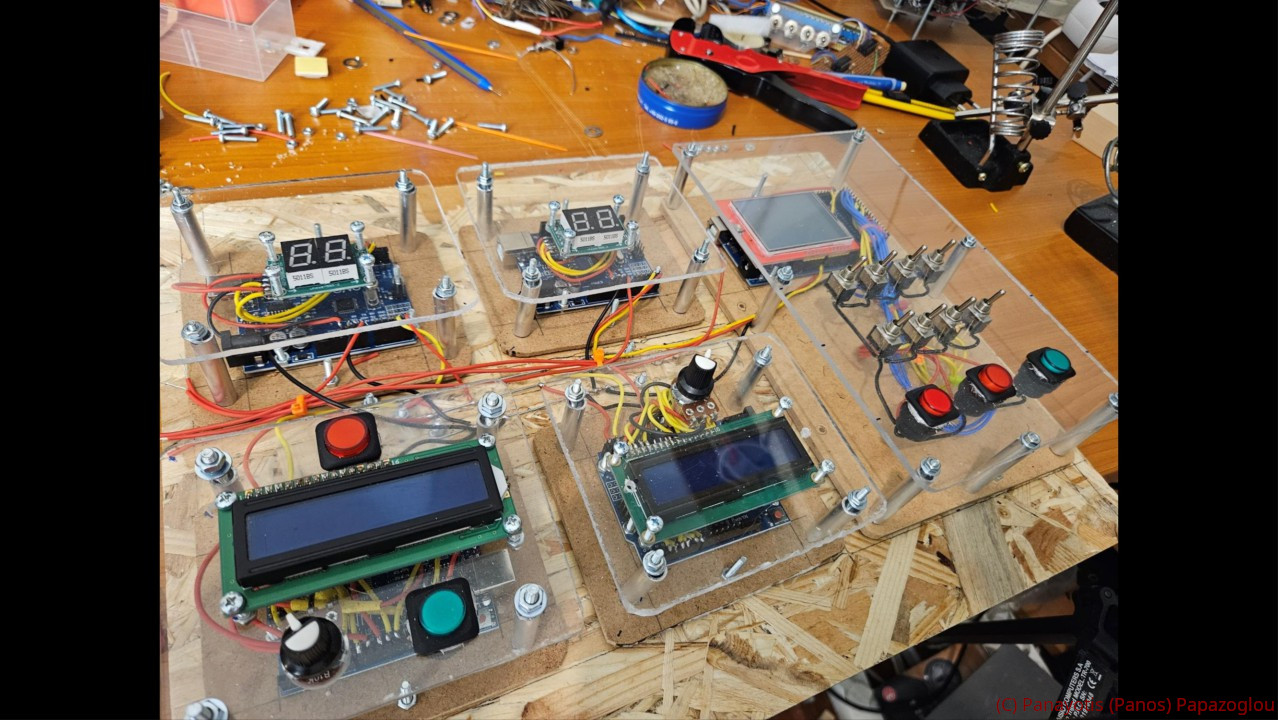

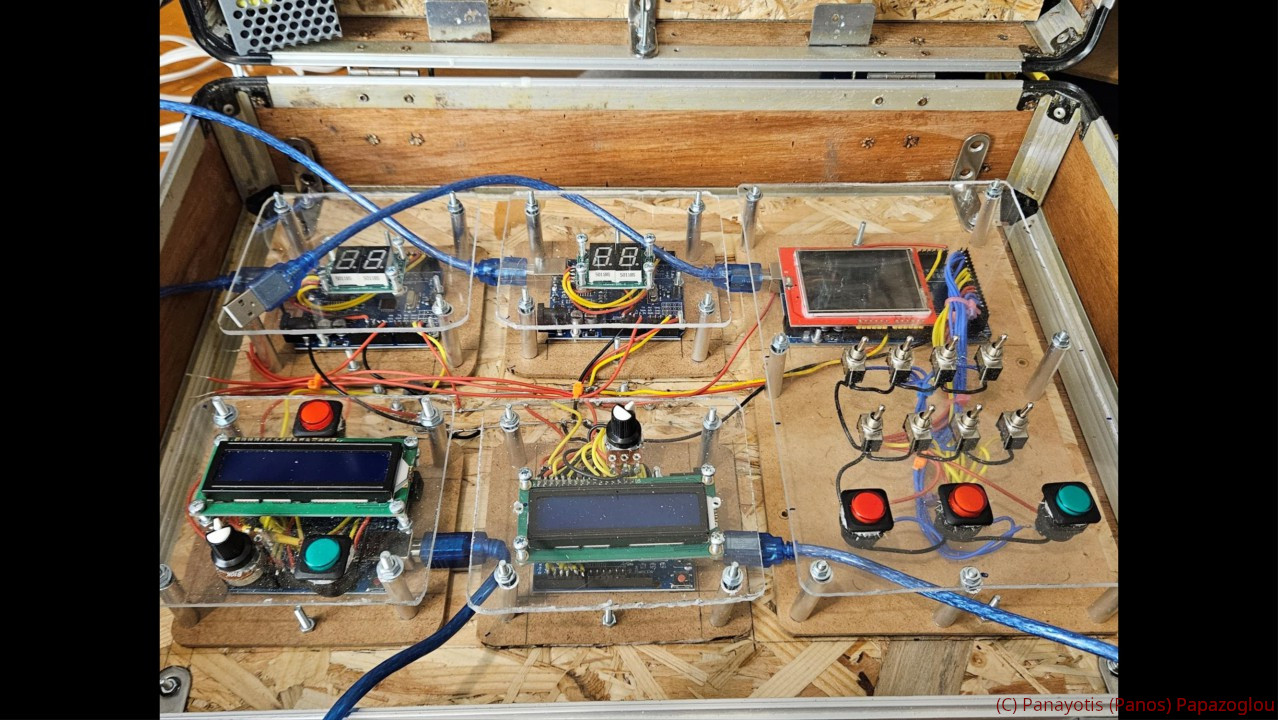

Begin your journey with version 1 of the hardware-oriented microprocessor simulator and explore a fully functional device where students can interact with and program the internal components of an experimental microprocessor.

Version 1 was presented at the IEEE EDUCON2024 conference in May 2024.

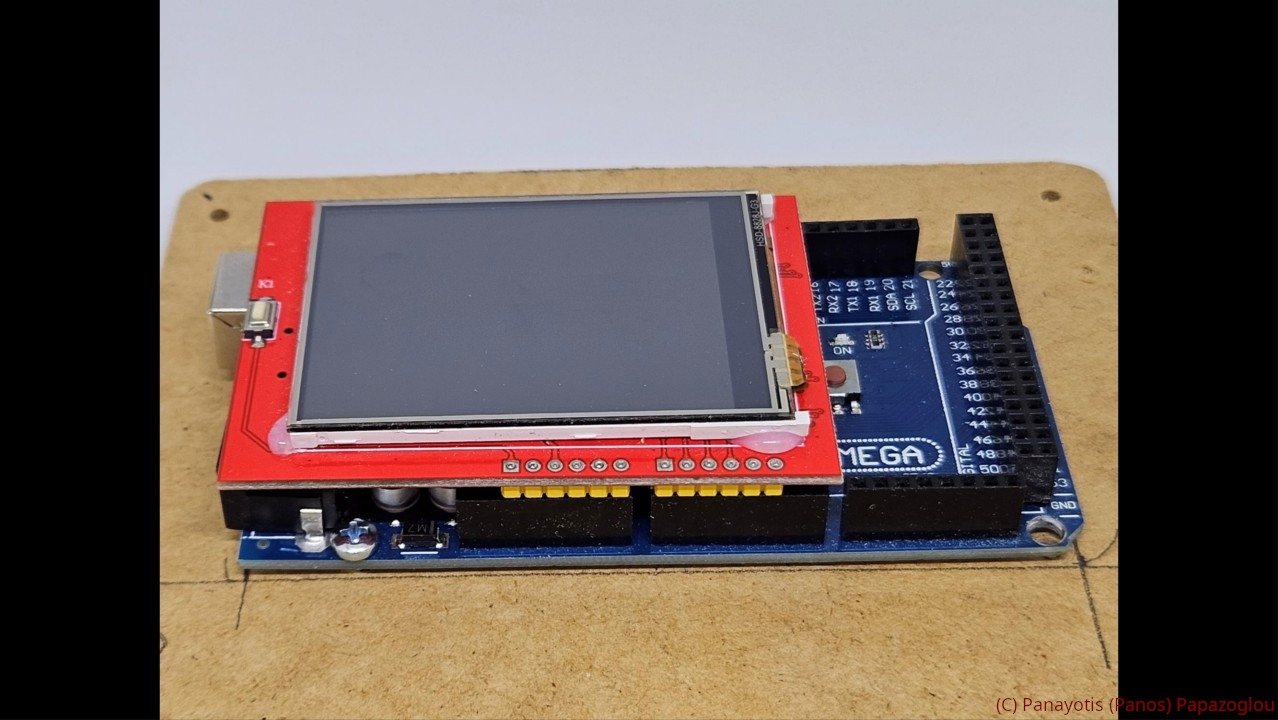

Version 2 is under construction.

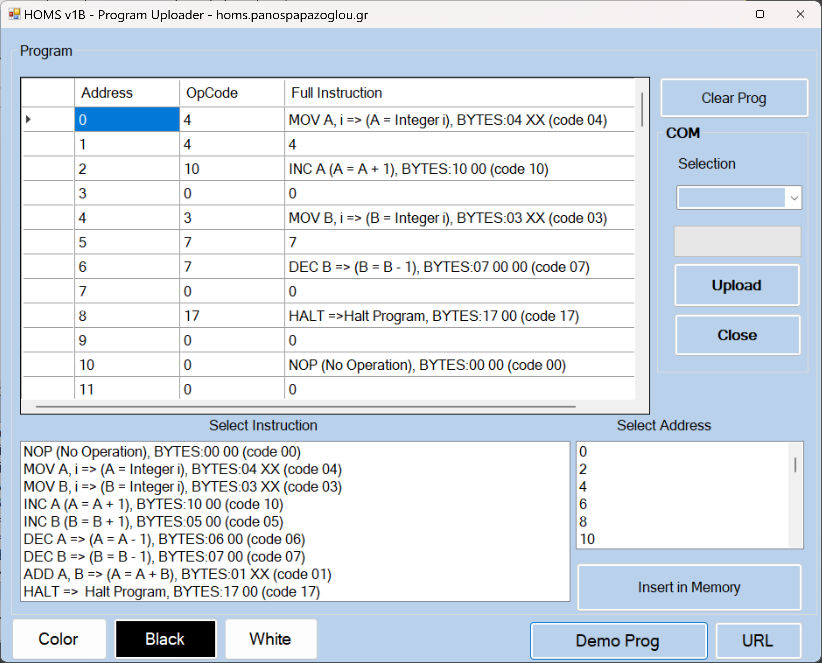

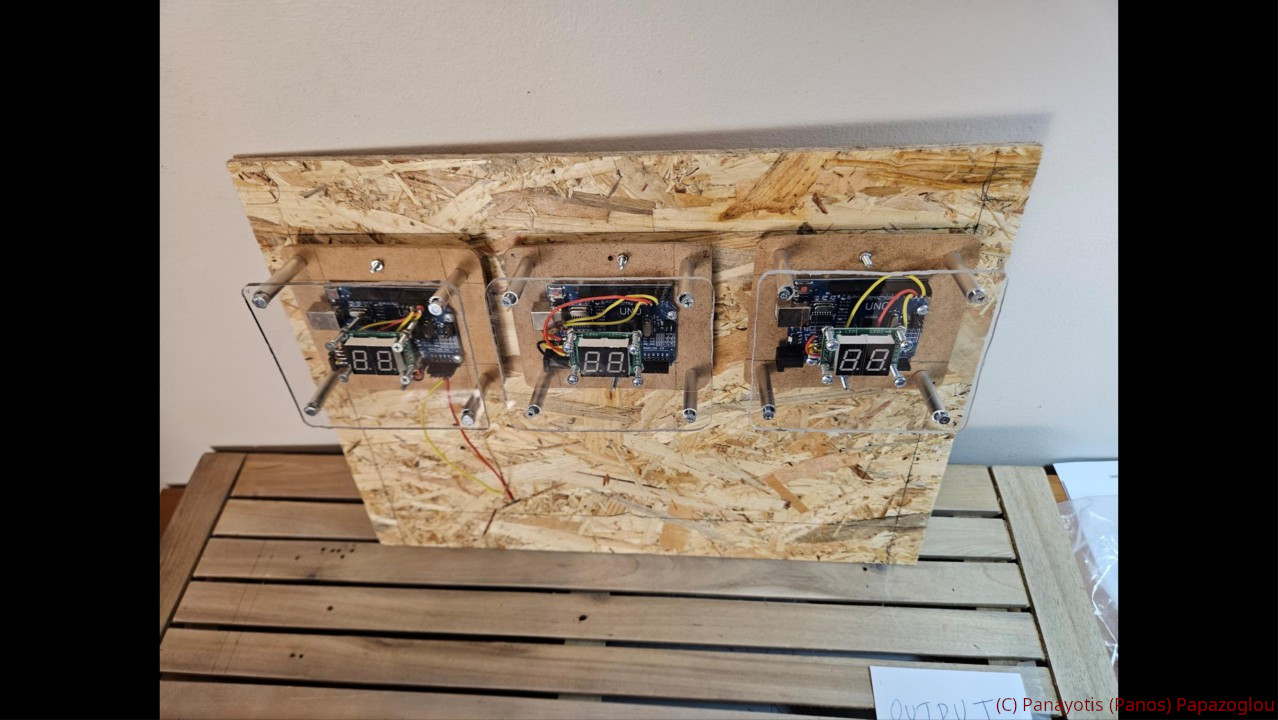

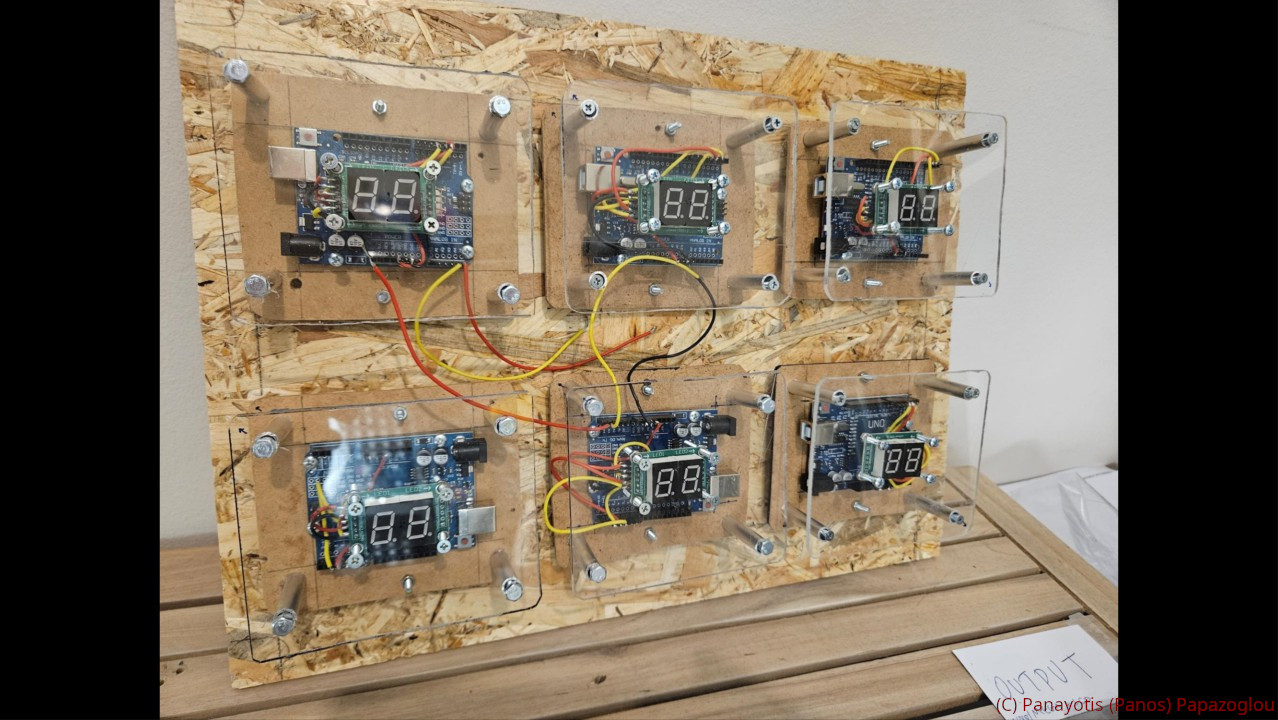

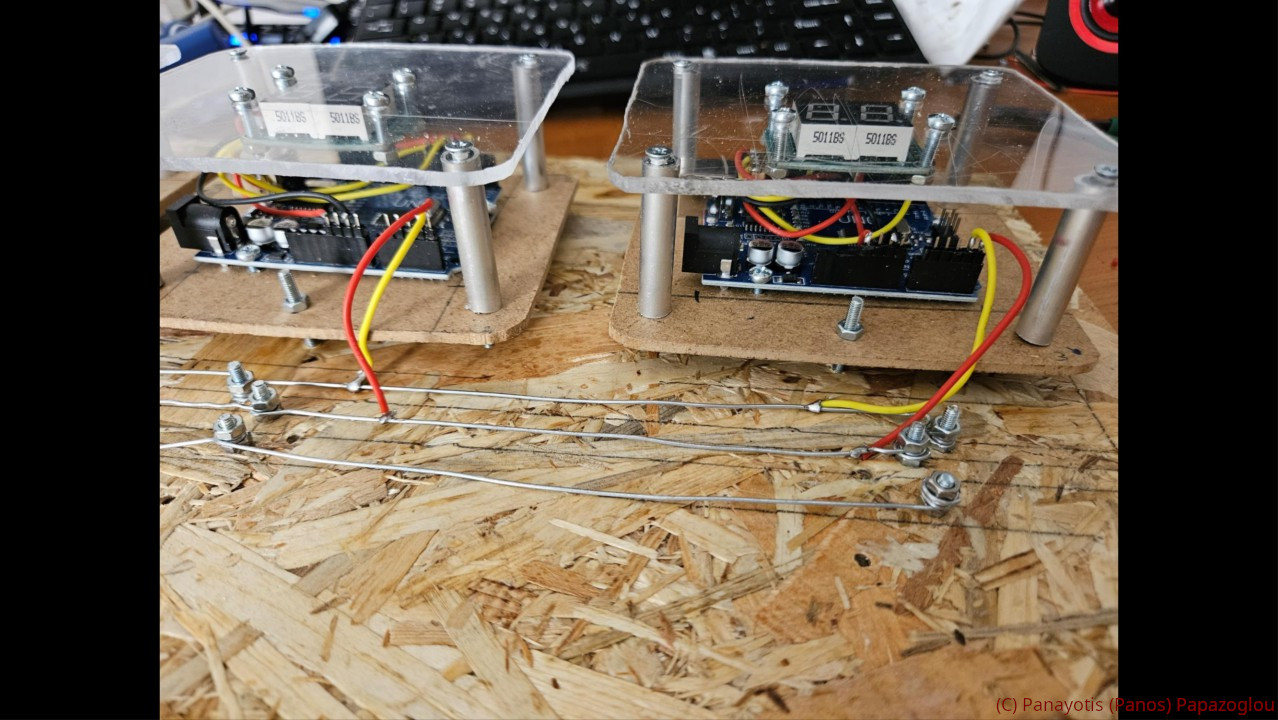

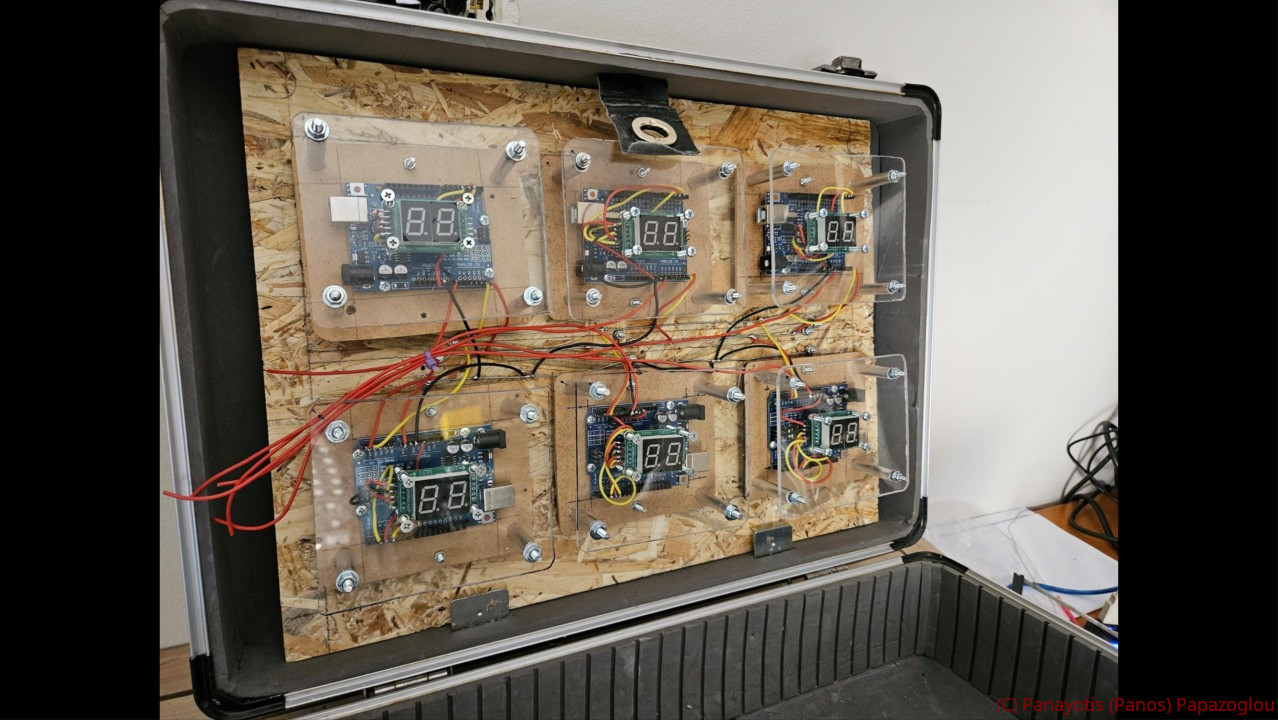

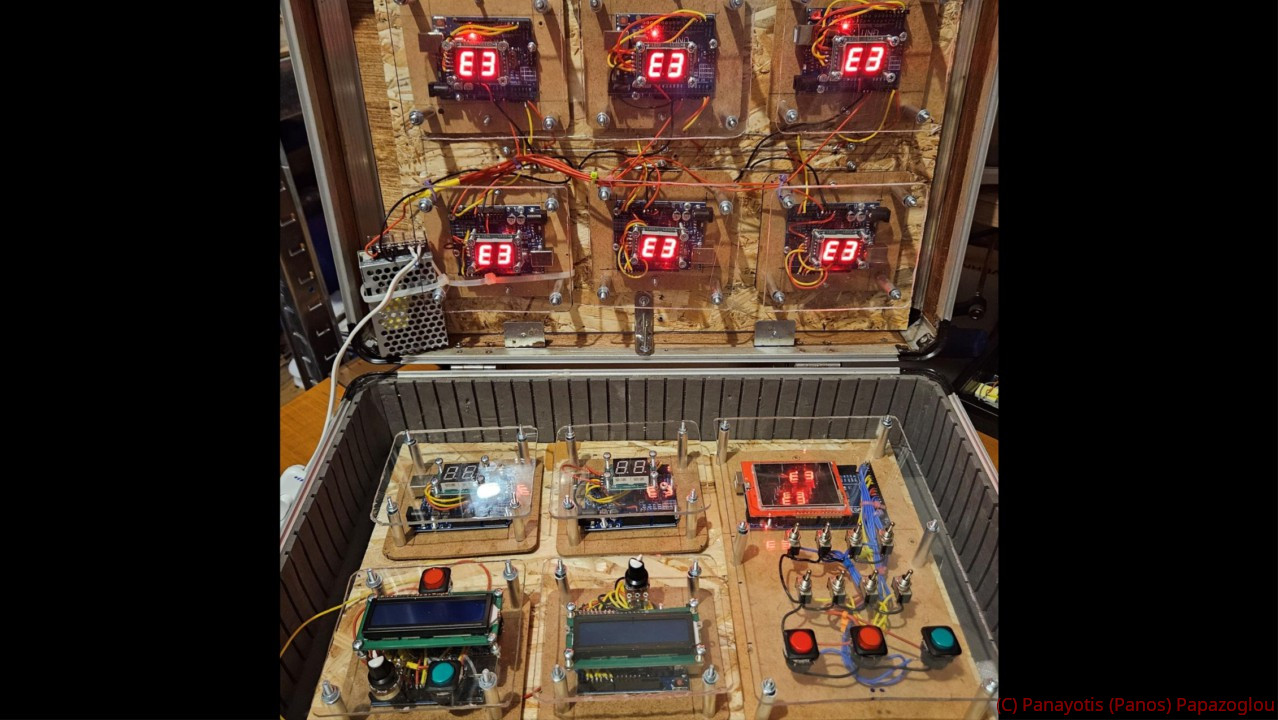

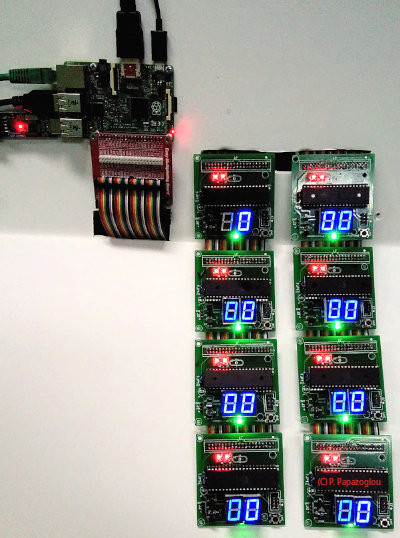

The teacher or student can use any number or type of blocks for building the preferred microprocessor architecture.

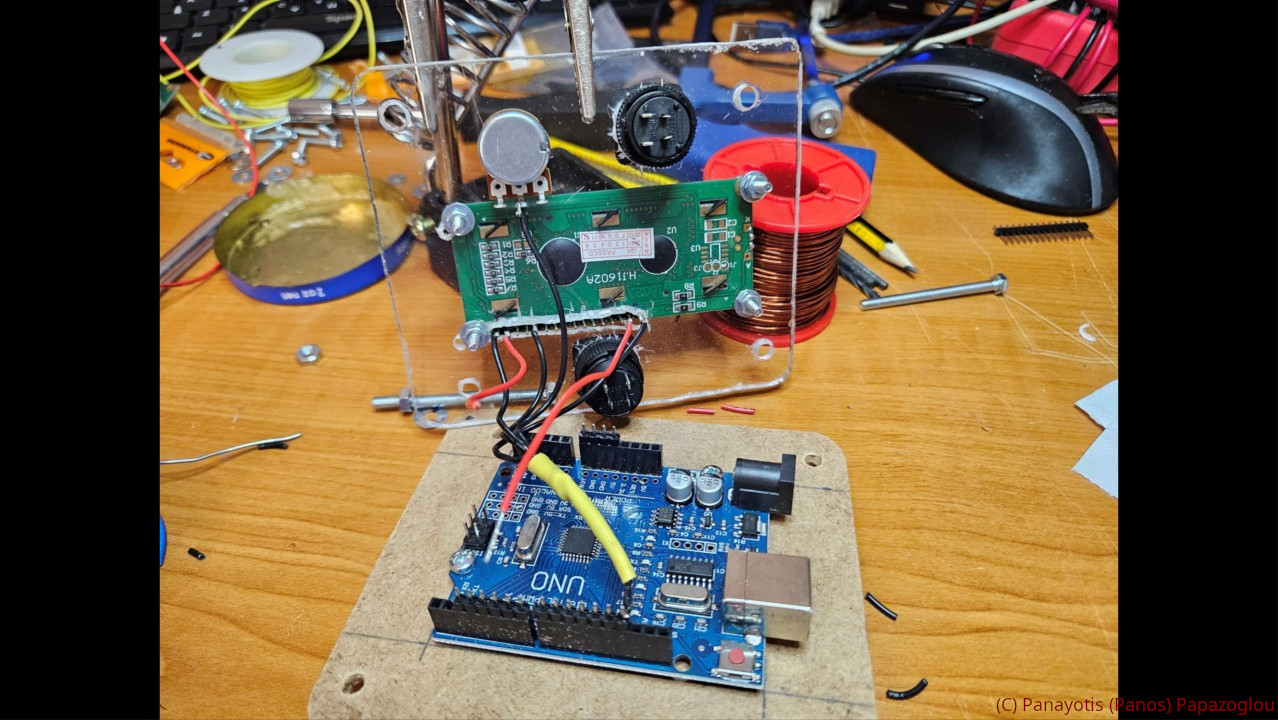

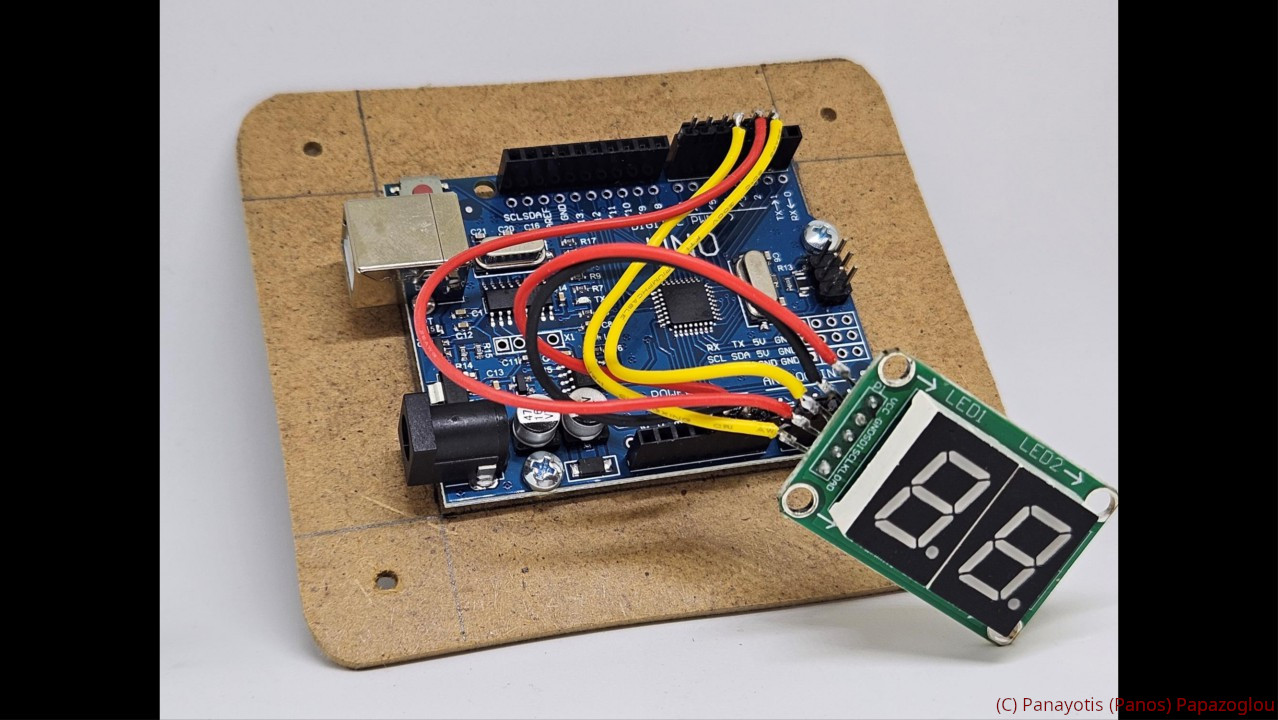

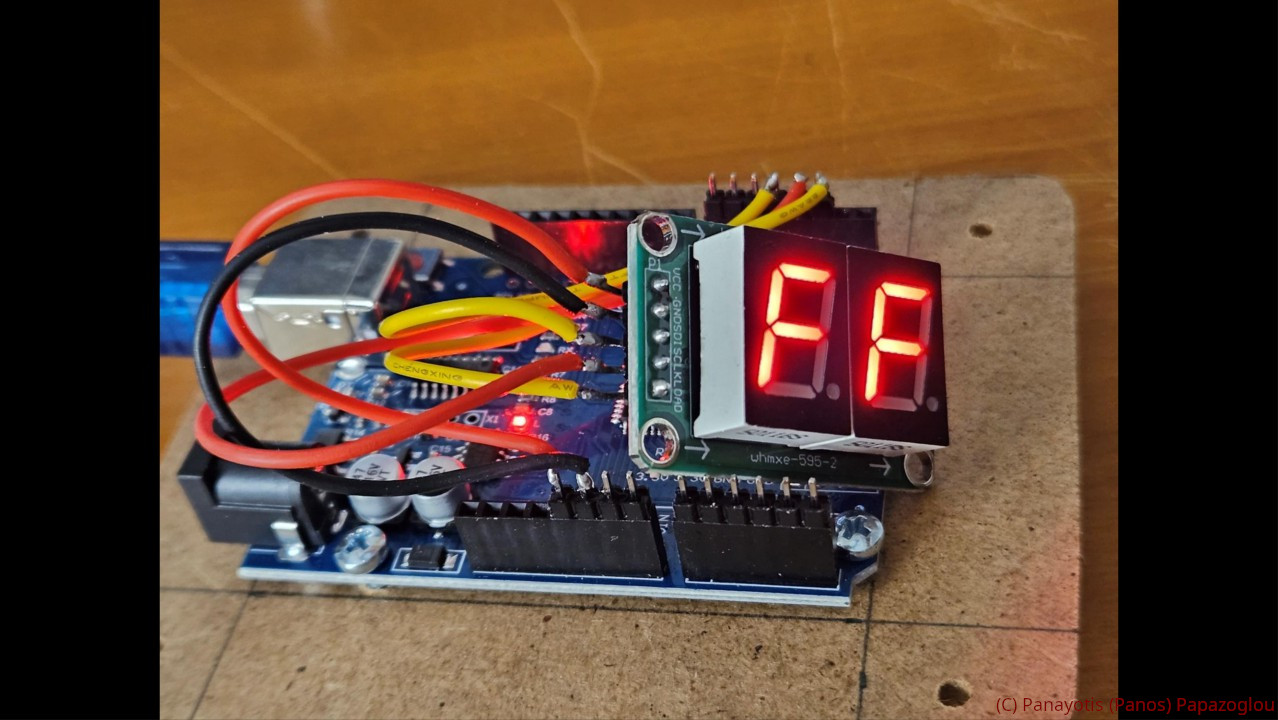

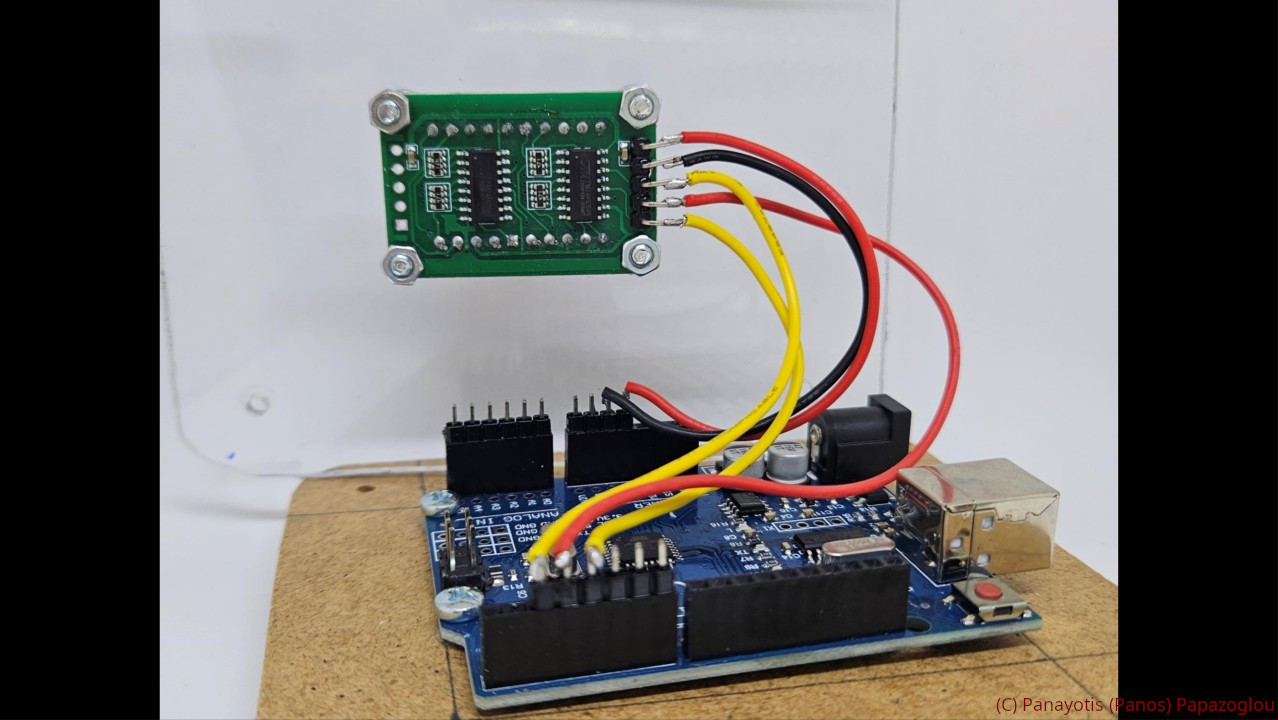

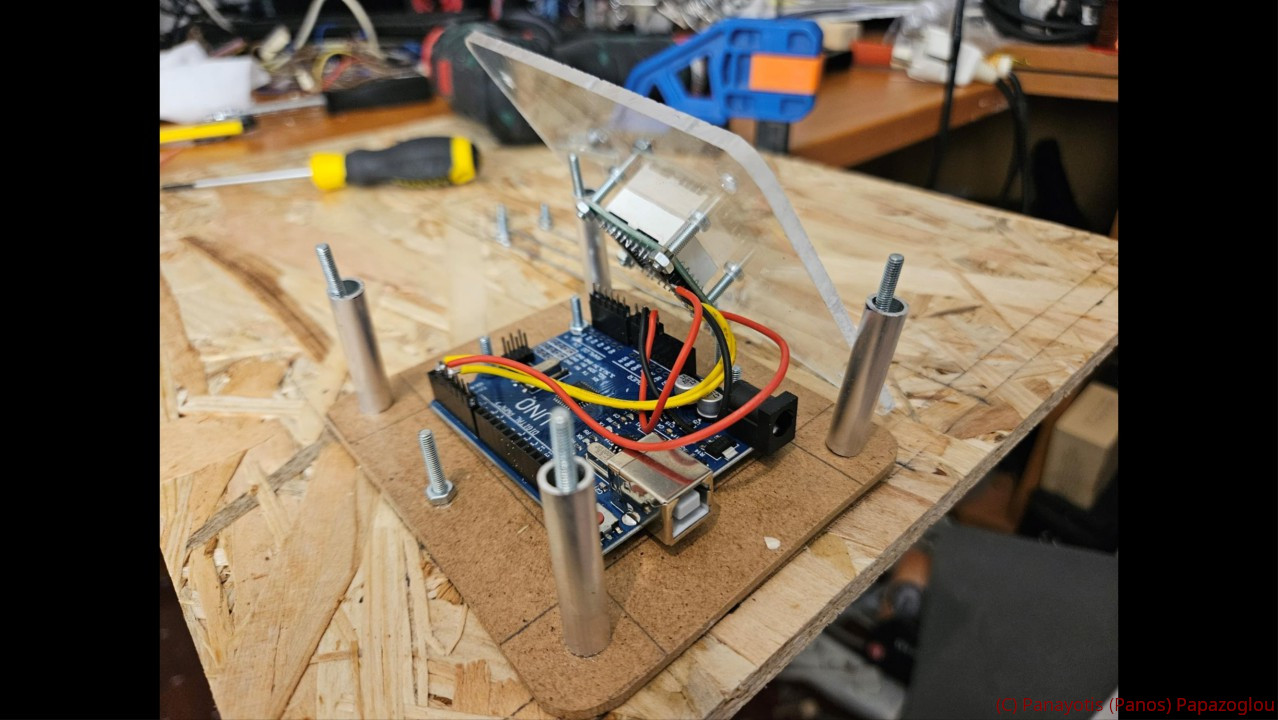

The microprocessor units are based on the same board and the embedded software determines the block functionality.

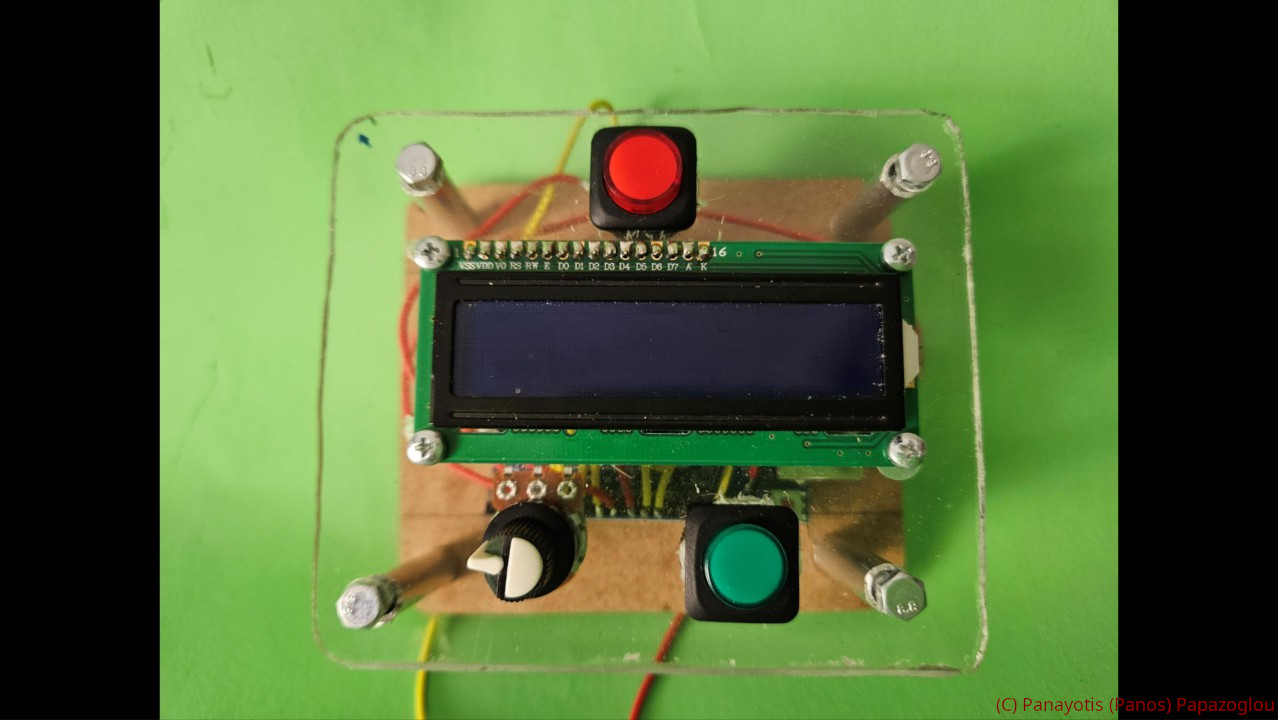

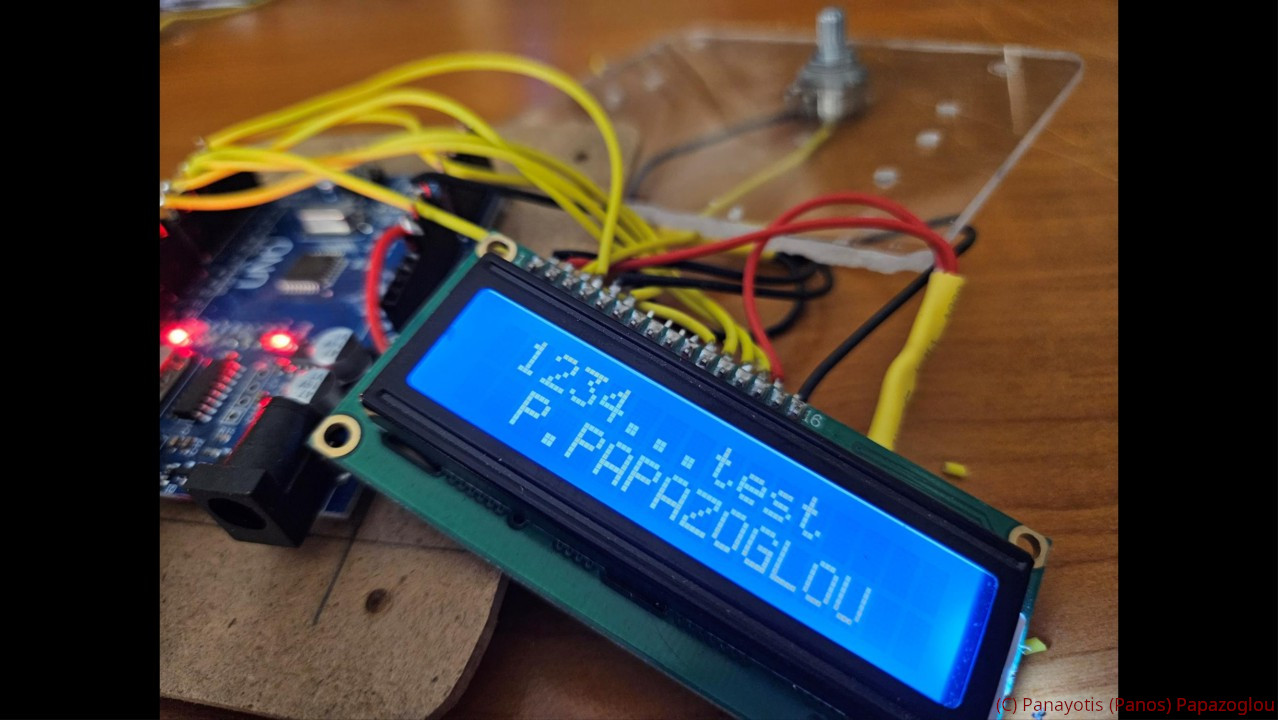

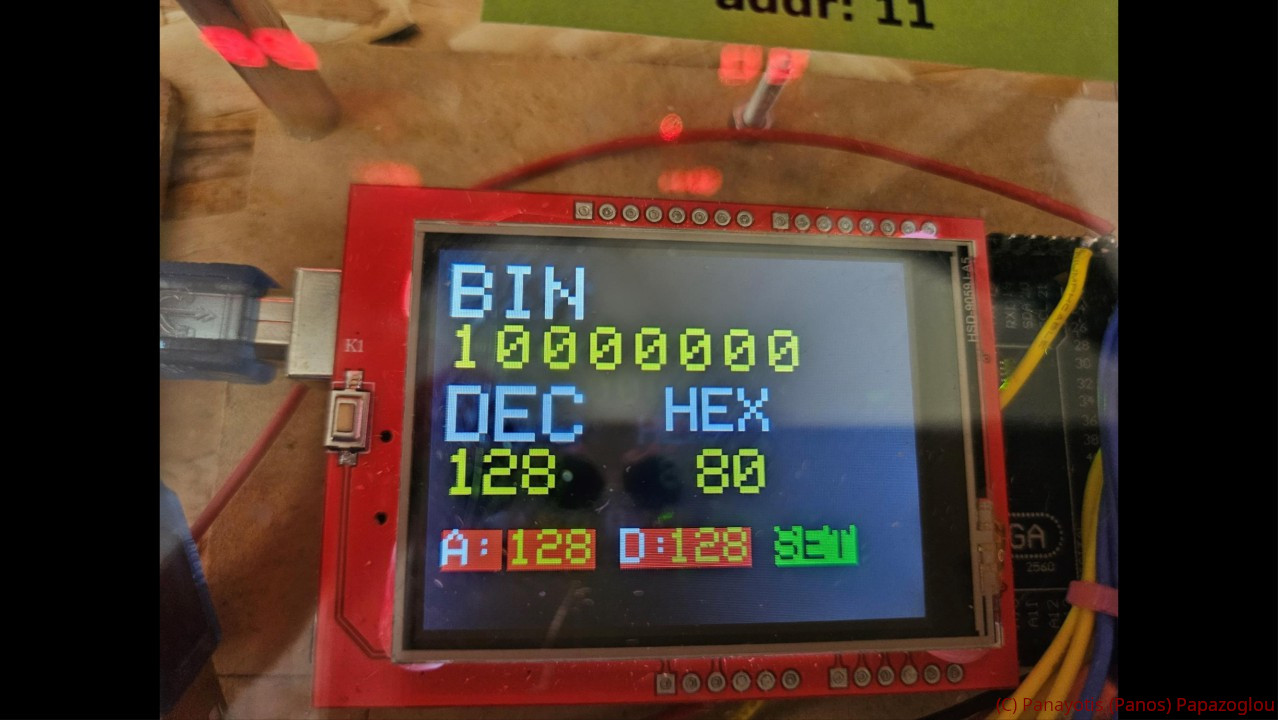

Based on the embedded software, a block operates like a register or control unit or ALU or special register, etc.

Based on the number and type of blocks, a teacher or student can test a prototype architecture or to expand an operation to smaller steps by using more blocks.

Programmer/user, Software/hardware developer, Watching/studying

The HOMS tool, emphasizes the hardware layer which is hidden in the existing simulation tools. Thus the “connection” of instruction, operation and hardware implementation is more clear in the student’s minds

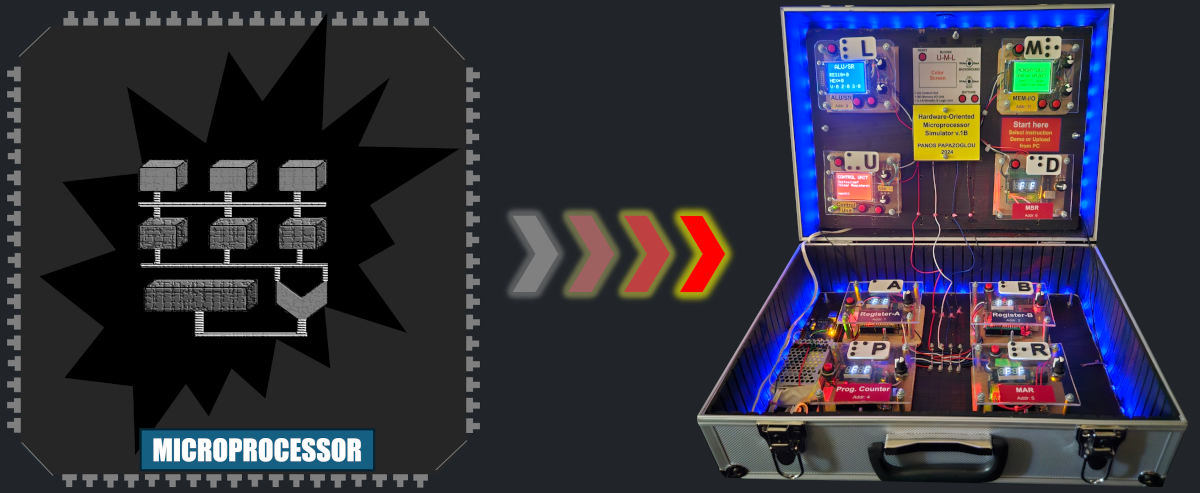

The HOMS user is free to build any assembly instruction which is supported by the software inside control unit.

Using the default HOMS tool architecture, teachers can develop the desired assembly instructions for building different educational scenarios.

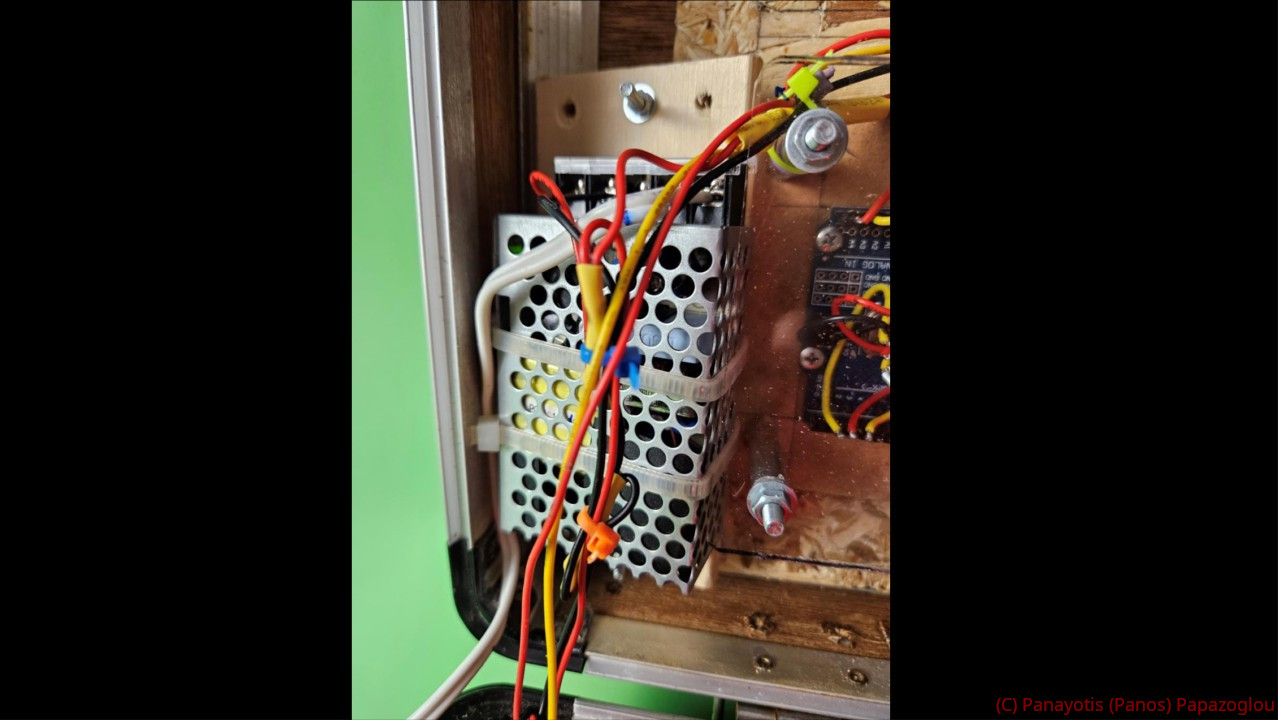

The proposed HOMS tool does not need a PC and can be operated autonomously. Thus, constitutes a mobile laboratory system unit

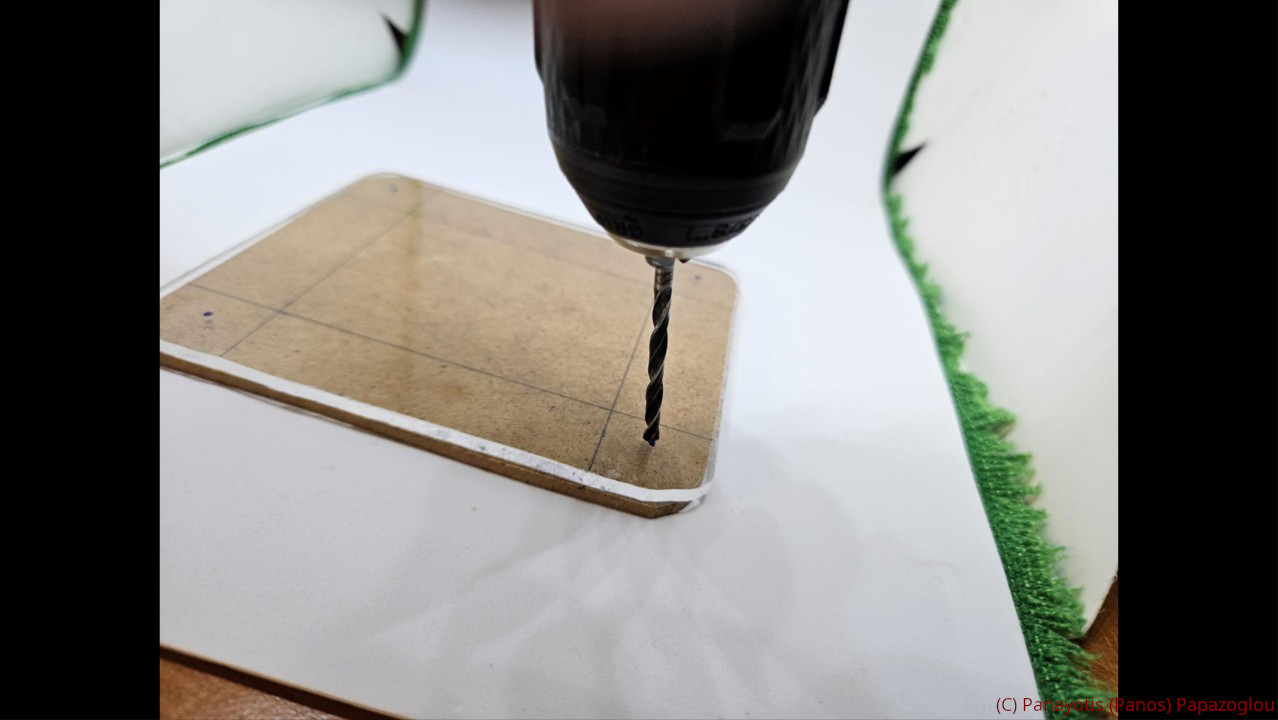

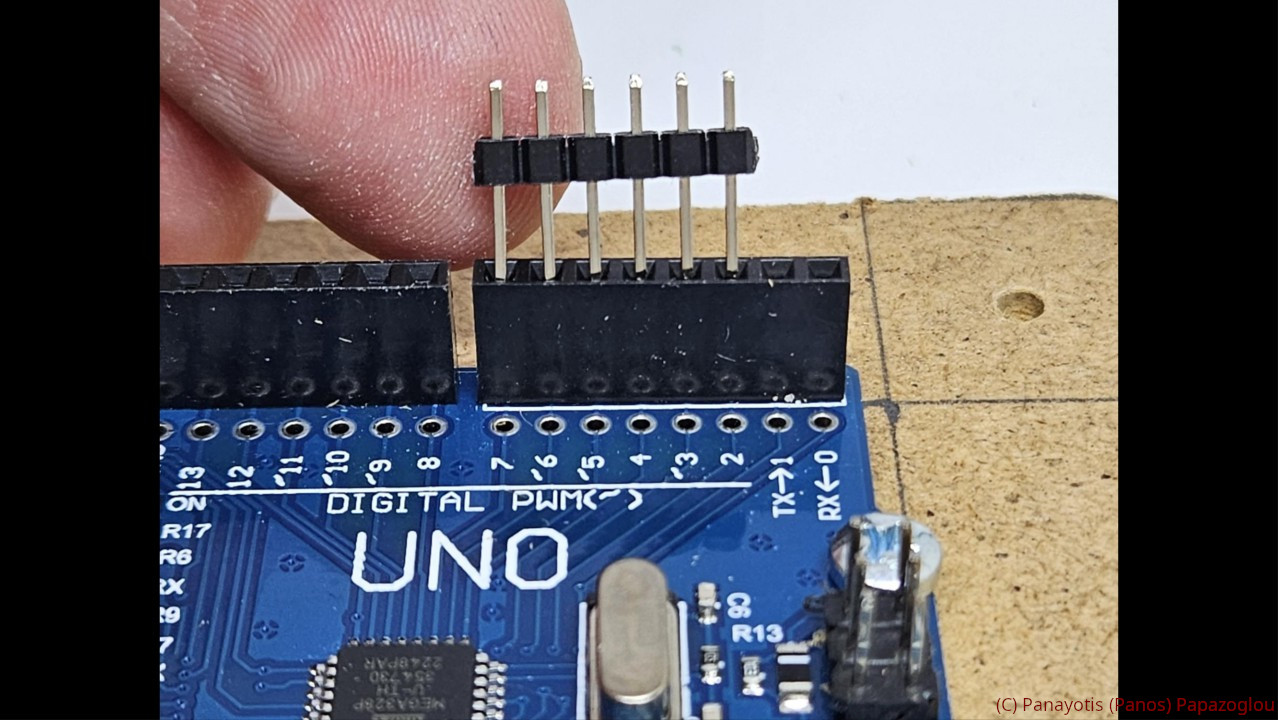

The hardware components of the HOMS tool can be found easily in any market. On the other hand, the multiple identical blocks support easily the reproduction procedure

The main advantage of the implemented HOMS tool is the object-oriented approach and the open-source hardware which gives the freedom to any developer not only to reproduce the same tool but also to implement the whole simulator using different blocks (with or without an LCD, buttons, etc). Note that the embedded software makes the difference.

General information, System description,System operation, Build reference (71 pages). View (PDF)

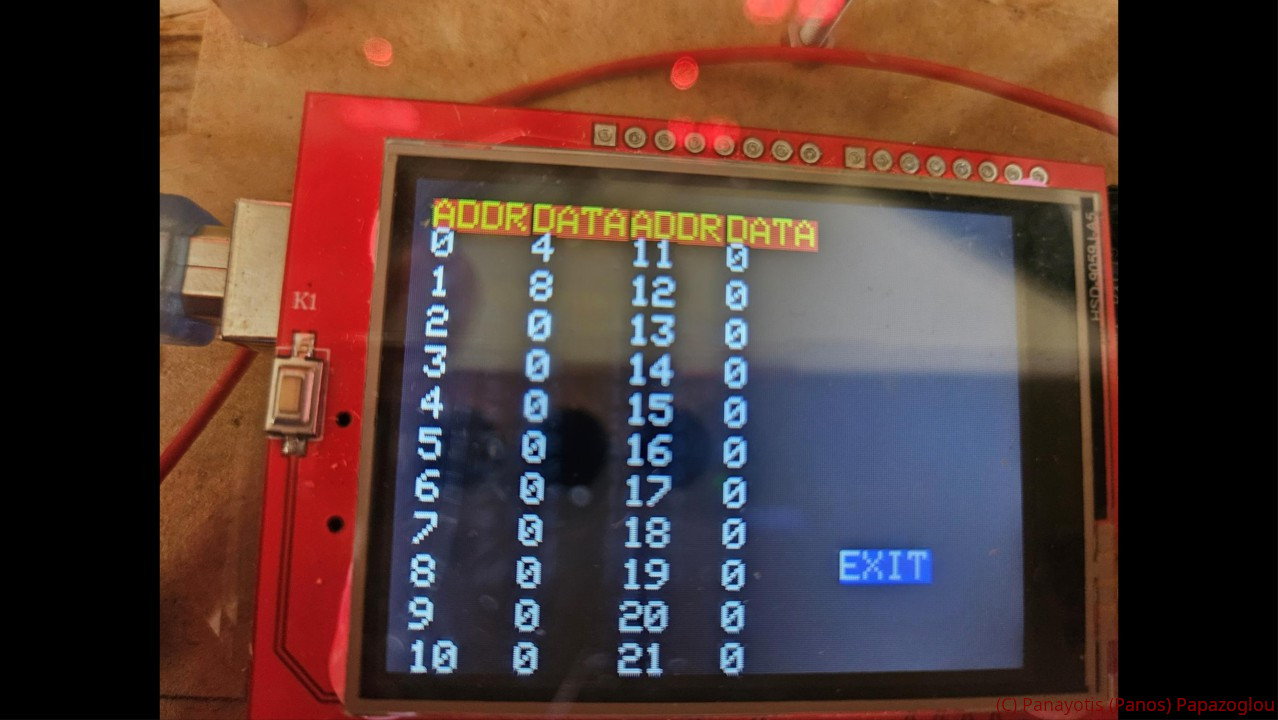

System map, Memory unit operation, Data entry, Code preload. View (PDF)

Arithmetic & Logic (ALU) Unit/SR, Control Unit (CU), Memory & I/O System, Registers, 7SD test. Download (ZIP)

Blocks A,B,C,D and System.

View all blocks-full (PDF)

View Block-A online (GPR/SPR)

View Block-B online (ALU/SR)

View Block-C online (CU)

View Block-D online (MEM-I/O)

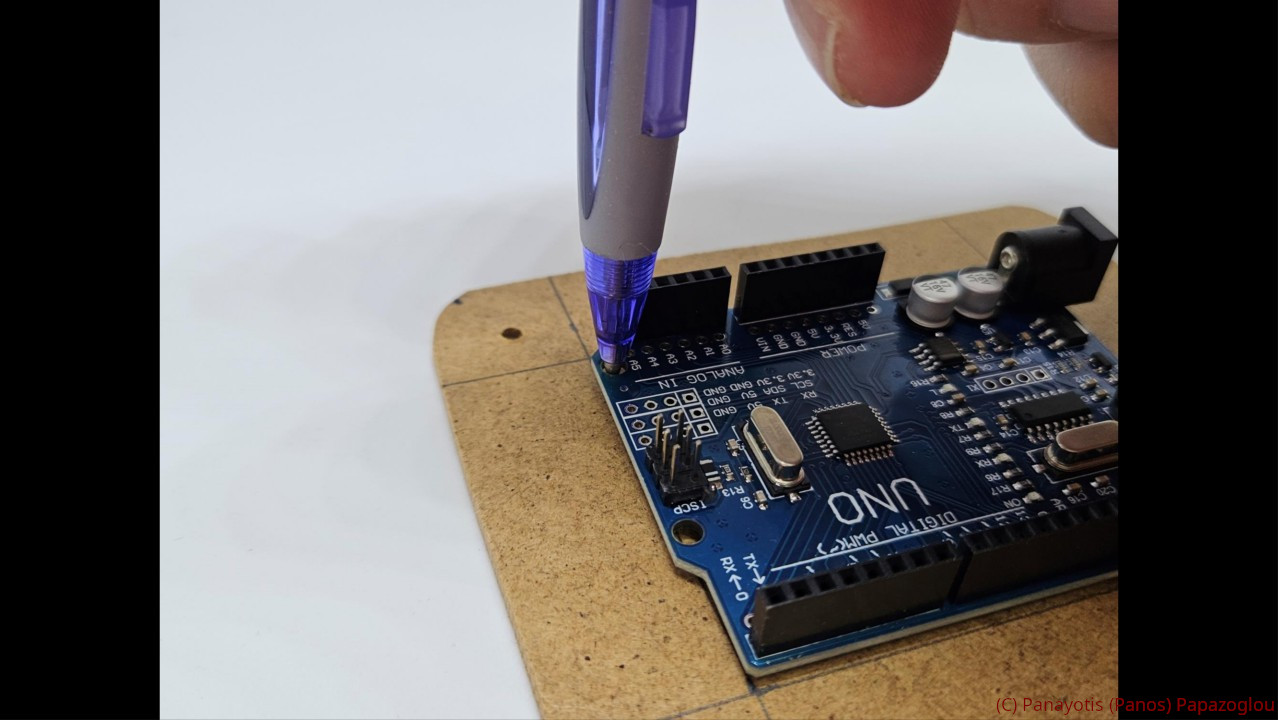

Components, materials, circuits, etc. View (PDF)

This is an open-source project under a CC license. This project has been also time stamped by HELLENIC COPYRIGHT ORGANIZATION (Date and time: 23/02/2024 22:57:22, Registration 5211). View license in TXT file or View license online

Version 1 was presented at the IEEE EDUCON2024 conference in May 2024.View file (PDF) || EDUCON 2024 on web

P.M.Papazoglou, A Hybrid Simulation Platform for Learning Microprocessors, Computer Applications in Engineering Education, 10.1002/cae.21921, (pp 655-674) WILEY, 2018 online

The proposed hybrid simulation platform (HSP) consists of hardware components which represent the uP architectural units and software components for system operation and administration.

Modern engineering applications are based on microprocessors and microcontrollers. Thus, the microprocessor (uP) architecture constitutes a core course component in engineering education. Many technologies have been used by the Universities in the past 30 years for learning uPs. In the 1980s, hardware platforms have been used (e.g., MPF-I) for learning assembly programming in hexadecimal mode of popular microprocessor models. The above platforms have been replaced by software simulators where the uP components are represented by visual objects. The software based approaches have lack of uP architecture customization and are limited only in assembly programming. On the other hand, the existing hardware based tools are low level and very complicated. Thus, the students do not work on uP design and assembly language development. In this paper, a novel hybrid simulator platform which changes the educational point of view regarding the uP learning methodology is presented. The proposed hybrid simulation platform (HSP) consists of hardware components which represent the uP architectural units and software components for system operation and administration. Using the HSP, students freely select the uP hardware based components and build their own architecture. On the other hand, professors can create educational scenarios with customizable experimental architectures.

P.M.Papazoglou, A Hybrid Simulation Platform for Learning Microprocessors, Computer Applications in Engineering Education, 10.1002/cae.21921, (pp 655-674) WILEY, 2018 online

Associate Professor Dr. Panayotis (Panos) Papazoglou

National and Kapodistrian University of Athens (NKUA)

Research Lab of Interactive Digital Systems

Dept. of Digital Arts and Cinema

contact: papaz [at] dcarts [dot] uoa [dot] gr

Copyright © Dr. Panayotis (Panos) Papazoglou